在人工智慧基礎設施半導體連線解決方案領域,Astera Labs 推出的 Leo 記憶體連接平台已為資料中心伺服器帶來空前的效能表現。該平台是業界首創,整合了 Compute Express Link (CXL)技術的記憶體控制器,在配合最新的第五代 Intel Xeon 可擴充處理器時,能將伺服器的總記憶體頻寬提高 50%,並且將反應時間減少 25% 。

這項創新由 Astera Labs 與 Intel 合作推出,有效突破了以往所謂的「記憶體牆」—一個長久以來影響伺服器性能的障礙。 Leo 平台透過最新的硬體設計,達成了 CXL 連線記憶體和中央處理器 (CPU)本地記憶體的交錯,使得應用程式無需任何修改即可享受更高的記憶體頻寬與容量,實現了即插即用的便利性。

Astera Labs 營運長 Sanjay Gajendra 指出,計算核心與性能的快速成長一直在超越記憶體頻寬的提升速度,這導致了伺服器效率隨著時間的推進而逐漸下降。但是,得益於與 Intel 的合作,Leo 記憶體連線平台成功克服了記憶體頻寬和延遲的挑戰。

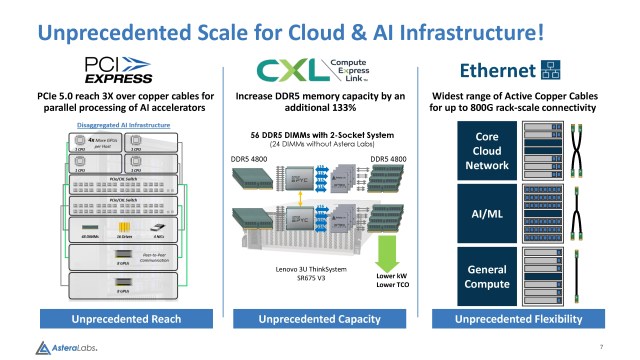

Astera Labs 資深副總 Thad Omura表示:「當我們探索當代計算基礎設施的進展時,記憶體、網路頻寬及資料傳輸速度已成為顯著的挑戰,這些瓶頸在 GPU 農場和 AI 平台的大規模部署中尤其明顯。以往我們依賴的傳統層次型架構已不敷使用,因為它們不適合 GPU 間高速連結的需求。現在,我們必須轉向網狀架構,這種架構可以實現 GPU 之間的直接且高速連接,這對於激發 AI 平台的最大潛力至關重要。」

Astera Labs 也透過推出 Aries PCIe 5.0 / CXL 2.0 智慧型重定時器 (Smart Retimers),進一步鞏固其在 PCIe 5.0 和 CXL 2.0 解決方案領域的領先地位。這些重定時器為市場上部署最廣、經過驗證的 PCIe/CXL 重定時器系列,並搭載低延遲 CXL 模式,與 Leo 記憶體控制器互補,共同構成了最強大的 CXL 記憶體連線解決方案。

Thad Omura 表示隨著 CXL 技術在 AI 平台上的足跡不斷擴大,記憶體牆問題在龐大工作負載下日益明顯。因此 Astera Labs 導入 CXL 記憶體控制器,同時提供遙測 (telemetry)功能,能夠即時提供伺服器與 GPU 之間連接效率表現的數據資料,協助雲端運算及超大規模運算客戶得以控制總體擁有成本,並最佳化系統運作的方式。